慈溪市天維通信設(shè)備廠 三網(wǎng)合一光分路器箱的專業(yè)制造商與供應(yīng)商

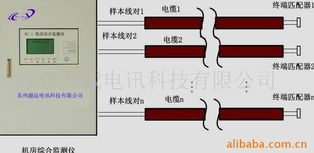

在當(dāng)今高速發(fā)展的信息化時代,通信網(wǎng)絡(luò)基礎(chǔ)設(shè)施的建設(shè)至關(guān)重要。其中,三網(wǎng)合一(即電信網(wǎng)、廣播電視網(wǎng)和互聯(lián)網(wǎng)的融合)是網(wǎng)絡(luò)發(fā)展的重要趨勢,它能夠有效整合資源、提升傳輸效率、降低建設(shè)和維護(hù)成本。而實現(xiàn)這一融合的關(guān)鍵物理設(shè)備之一,便是光分路器箱。作為連接光纜、實現(xiàn)光信號分路與分配的核心節(jié)點,其性能與可靠性直接影響到整個網(wǎng)絡(luò)的穩(wěn)定運(yùn)行。

在眾多生產(chǎn)廠商中,位于浙江省慈溪市的慈溪市天維通信設(shè)備廠,憑借其專業(yè)的技術(shù)實力和穩(wěn)定的產(chǎn)品質(zhì)量,在光通信設(shè)備領(lǐng)域樹立了良好的口碑,成為了三網(wǎng)合一光分路器箱重要的廠家與供應(yīng)商之一。

一、專業(yè)聚焦,深耕光通信領(lǐng)域

慈溪市天維通信設(shè)備廠專注于光無源器件及配線設(shè)備的研發(fā)、生產(chǎn)與銷售。對于三網(wǎng)合一光分路器箱,廠家有著深入的理解和豐富的制造經(jīng)驗。這類設(shè)備通常需要滿足高密度安裝、靈活配置、良好的防護(hù)性能(如防水、防塵、抗腐蝕)以及便于施工和維護(hù)等要求。天維通信依托成熟的生產(chǎn)工藝和嚴(yán)格的質(zhì)量控制體系,能夠提供從標(biāo)準(zhǔn)型號到定制化解決方案的全系列產(chǎn)品,滿足不同規(guī)模網(wǎng)絡(luò)建設(shè)(如FTTH光纖到戶、樓宇布線、園區(qū)網(wǎng)絡(luò))的需求。

二、產(chǎn)品核心優(yōu)勢與計算機(jī)輔助設(shè)計

“計算機(jī)輔助設(shè)備”在提示詞中的出現(xiàn),恰恰點明了現(xiàn)代制造業(yè),尤其是精密通信設(shè)備制造的核心競爭力所在。慈溪市天維通信設(shè)備廠在生產(chǎn)過程中,廣泛應(yīng)用了計算機(jī)輔助設(shè)計(CAD)、計算機(jī)輔助工程(CAE)和計算機(jī)輔助制造(CAM)等先進(jìn)技術(shù)。

- 設(shè)計與仿真:利用CAD軟件進(jìn)行產(chǎn)品結(jié)構(gòu)、內(nèi)部走線路徑、散熱布局等的精細(xì)化設(shè)計,確保箱體結(jié)構(gòu)合理、空間利用率高。通過CAE軟件對產(chǎn)品的機(jī)械強(qiáng)度、防護(hù)等級等進(jìn)行模擬仿真,優(yōu)化設(shè)計,提升產(chǎn)品在復(fù)雜環(huán)境下的可靠性。

- 精密制造:CAM技術(shù)將設(shè)計方案無縫轉(zhuǎn)換為生產(chǎn)指令,驅(qū)動高精度數(shù)控機(jī)床、注塑機(jī)等設(shè)備進(jìn)行加工,保證了箱體、適配器面板、光纖熔接盤等零部件的尺寸精確度和一致性,為后續(xù)的高質(zhì)量組裝奠定基礎(chǔ)。

- 質(zhì)量管控:計算機(jī)輔助的檢測設(shè)備也被用于生產(chǎn)環(huán)節(jié),對光學(xué)性能(如插入損耗、分光比均勻性)、物理性能進(jìn)行自動化測試,確保每一臺出廠的光分路器箱都符合甚至超越行業(yè)標(biāo)準(zhǔn)。

這種深度融合的計算機(jī)輔助生產(chǎn)模式,使得天維通信的產(chǎn)品在工藝精度、生產(chǎn)效率和品質(zhì)穩(wěn)定性方面具備了顯著優(yōu)勢。

三、作為供應(yīng)商的價值

作為供應(yīng)商,慈溪市天維通信設(shè)備廠不僅提供產(chǎn)品,更提供配套服務(wù)。他們能夠根據(jù)客戶的具體項目需求,提供產(chǎn)品選型咨詢、技術(shù)方案支持。其供貨渠道穩(wěn)定,生產(chǎn)計劃靈活,能夠響應(yīng)市場變化和客戶的緊急需求。位于長三角經(jīng)濟(jì)活躍區(qū)的地理位置,也使其在物流配送和服務(wù)響應(yīng)上具有便利性。

四、市場應(yīng)用與展望

三網(wǎng)合一光分路器箱廣泛應(yīng)用于運(yùn)營商網(wǎng)絡(luò)、智能城市建設(shè)、企業(yè)專網(wǎng)、酒店及住宅小區(qū)寬帶接入等多個場景。隨著5G網(wǎng)絡(luò)建設(shè)的深入推進(jìn)和“雙千兆”網(wǎng)絡(luò)(千兆光網(wǎng)和5G)的普及,對高性能、高可靠性的光配線設(shè)備需求將持續(xù)增長。慈溪市天維通信設(shè)備廠作為產(chǎn)業(yè)鏈中的重要一環(huán),通過持續(xù)的技術(shù)創(chuàng)新和工藝改進(jìn),正不斷鞏固和擴(kuò)大其市場地位,為構(gòu)建更高效、更智能的融合通信網(wǎng)絡(luò)貢獻(xiàn)著力量。

慈溪市天維通信設(shè)備廠是一家集研發(fā)、生產(chǎn)、銷售于一體的專業(yè)通信設(shè)備制造商,其利用先進(jìn)的計算機(jī)輔助設(shè)計制造技術(shù)生產(chǎn)的三網(wǎng)合一光分路器箱,以可靠的品質(zhì)和專業(yè)的服務(wù),成為了市場信賴的選擇,助力著中國乃至全球光通信網(wǎng)絡(luò)的基礎(chǔ)設(shè)施建設(shè)。

如若轉(zhuǎn)載,請注明出處:http://www.e7752.cn/product/52.html

更新時間:2026-03-09 05:42:06